The TSMC Toll Road

In Apple’s most recently completed full fiscal year (FY2025), total net sales reached $416.16 billion. But examining the core devices strictly reliant on TSMC-manufactured silicon reveals a dangerous dependency.

These three product lines alone generated $271.32 billion, accounting for exactly 65.2% of Apple's entire global revenue. Factoring in "Wearables, Home and Accessories" segments, Apple's direct revenue dependence on TSMC's factories climbs to nearly 74%.

The industry baseline cost for a current-generation 3nm (N3) wafer averages $25,000. For the bleeding-edge 2-nanometer (N2) process—requiring a massive architectural shift to Gate-All-Around (GAA) nanosheets—TSMC has established a firm new price floor of $30,000 per wafer.

This represents an exact 20% price increase over the 3nm baseline (and a staggering 66% jump compared to the original $18,000 price point of its 5nm nodes).

TSMC’s monopoly on angstrom-scale yield allows them to uniformly enforce this premium without offering Apple its traditional volume discounts.

A historic paradigm shift was formalized in TSMC's early 2026 annual reporting: For the first time in over a decade, Nvidia officially dethroned Apple as TSMC's #1 customer.

Projected to hit 22% / $33B in 2026

Down from historical highs of 22%–25%

The Takeaway

High-Performance Computing (HPC) for AI now dominates TSMC's revenue. Apple no longer dictates the roadmap because AI hyperscalers are willing to pay any premium for capacity.

To maintain its manufacturing monopoly, TSMC's projected Capital Expenditure (CAPEX) for 2026 is an astronomical $52 billion to $56 billion.

To contextualize this barrier to entry, a single next-generation ASML High-NA EUV lithography machine (the Twinscan EXE:5200) costs approximately $380 million.

TSMC’s annual infrastructure budget is the financial equivalent of buying roughly 135 to 147 of the most complex, expensive machines in human history every single year.

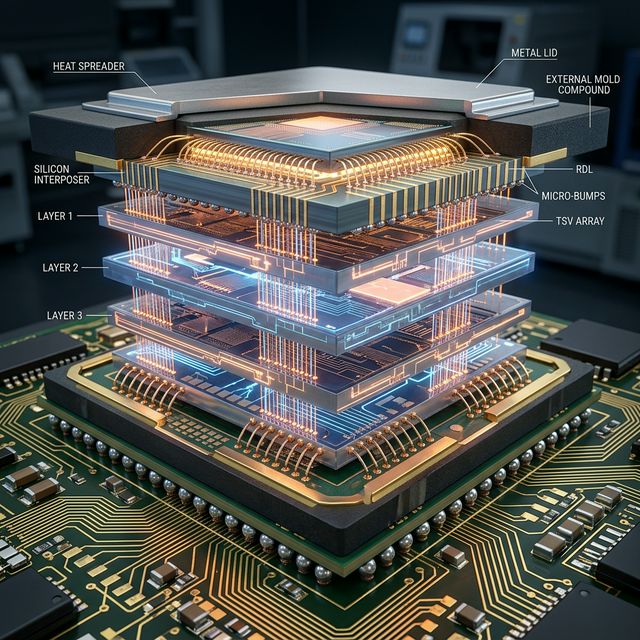

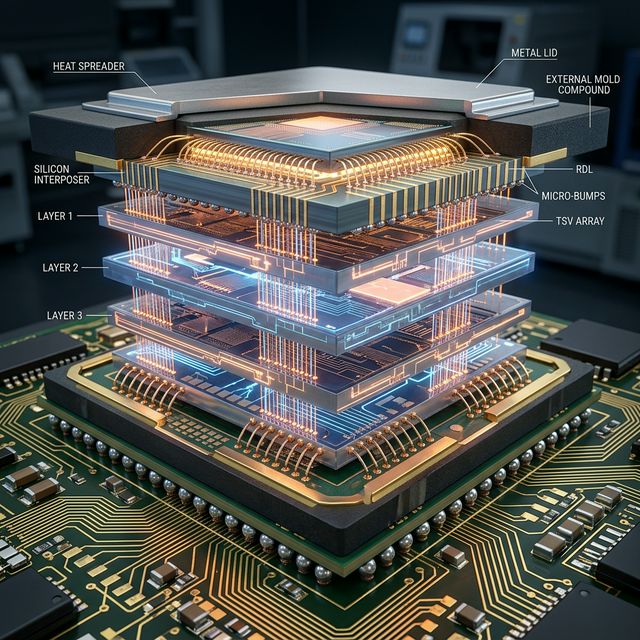

TSMC holds a near-monopoly on high-end advanced packaging, commanding >90% market share for the Chip-on-Wafer-on-Substrate (CoWoS) technology required to stitch logic chips and High-Bandwidth Memory (HBM) together.

TSMC executives have confirmed that CoWoS capacity is structurally "sold out through 2026."

Even as TSMC aggressively scales output to over 100,000 wafers per month, supply chain analysts estimate a massive deficit of up to 400,000 wafers in 2026. Nvidia alone is absorbing roughly 60% of that capacity, leaving consumer tech giants fighting for the scraps.

While Apple flaunts an impressive overall gross margin of ~47%, it is a smokescreen subsidized by its Software Services segment (75.3% margin). Apple’s actual Hardware (Products) gross margin faces continuous volatility:

Analysts warn that TSMC's $30,000 2nm wafers act as a massive structural headwind. In a highly saturated smartphone market, Apple lacks the pricing power to hike retail prices enough to offset the manufacturing premium, threatening to permanently compress hardware margins.

The broader stock market is aggressively pricing in this shift in the tech hierarchy. Looking at the exact 24-month window from March 2024 to March 2026:

Apple (AAPL)

$2.65T → $3.68T

~39% Growth

TSMC (TSM)

$690B → $1.75T

>150% Growth

Institutional capital is flowing toward the base layer of the pyramid. While Apple continues to sell the spectacle of the digital economy, the market recognizes that TSMC owns the toll road—and they are raising the rent.